- Important aspect of computer – design of the instruction set for processor.

- Instruction set – determines the way that machine language programs are constructed.

- Early computers – simple and small instruction set, need to minimize the hardware used.

- Advent of IC – cheaper digital software, instructions intended to increase both in number of complexity.

- Many computers – more than 100 or 200 instructions, variety of data types and large number of addressing modes.

Complex Instruction Set Computers (CISC)

- The trend into computer hardware complexity was influenced by various factors:

- Upgrading existing models to provide more customer applications

- Adding instructions that facilitate the translation from high-level language into machine language programs

- Striving to develop machines that move functions from software implementation into hardware implementation

- A computer with a large number of instructions is classified as a complex instruction set computer (CISC).

- One reason for the trend to provide a complex instruction set is the desire to simplify the compilation and improve the overall computer performance.

- The essential goal of CISC architecture is to attempt to provide a single machine instruction for each statement that is written in a high-level language.

- Examples of CISC architecture are the DEC VAX computer and the IBM 370 Other are 8085, 8086, 80x86 etc.

The major characteristics of CISC architecture

- A large number of instructions– typically from 100 to 250 instructions

- Some instructions that perform specialized tasks and are used infrequently

- A large variety of addressing modes—typically from 5 to 20 different modes

- Variable-length instruction formats

- Instructions that manipulate operands in memory

- Reduced speed due to memory read/write operations

- Use of microprogram – special program in control memory of a computer to perform the timing and sequencing of the microoperations – fetch, decode, execute etc.

- Major complexity in the design of microprogram

- No large number of registers – single register set of general purpose and low cost

Reduced Instruction Set Computers (RISC)

A computer uses fewer instructions with simple constructs so they can be executed much faster within the CPU without having to use memory as often. It is classified as a reduced instruction set computer (RISC).

- RISC concept – an attempt to reduce the execution cycle by simplifying the instruction set

- Small set of instructions – mostly register to register operations and simple load/store operations for memory access

- Each operand – brought into register using load instruction, computations are done among data in registers and results transferred to memory using store instruction

- Simplify instruction set and encourages the optimization of register manipulation

- May include immediate operands, relative mode etc.

The major characteristics of RISC architecture

- Relatively few instructions

- Relatively few addressing modes

- Memory access limited to load and store instructions

- All operations done within the registers of the CPU

- Fixed-length, easily decoded instruction format

- Single-cycle instruction execution

- Hardwired rather than microprogrammed control

Other characteristics attributed to RISC architecture

- A relatively large number of registers in the processor unit

- Use of overlapped register windows to speed-up procedure call and return

- Efficient instruction pipeline – fetch, decode and execute overlap

- Compiler support for efficient translation of high-level language programs into machine language programs

- Studies that show improved performance for RISC architecture do not differentiate between the effects of the reduced instruction set and the effects of a large register file.

- A large number of registers in the processing unit are sometimes associated with RISC processors.

- RISC processors often achieve 2 to 4 times the performance of CISC processors.

- RISC uses much less chip space; extra functions like memory management unit or floating point arithmetic unit can also be placed on same Smaller chips allow a semiconductor mfg. to place more parts on a single silicon wafer, which can lower the per chip cost dramatically.

- RISC processors are simpler than corresponding CISC processors, they can be designed more quickly.

Overlapped register windows

- Some computers provide multiple-register banks, and each procedure is allocated its own bank of This eliminates the need for saving and restoring register values.

- Some computers use the memory stack to store the parameters that are needed by the procedure, but this required a memory access every time the stack is accessed.

- A characteristic of some RISC processors is their use of overlapped register windows to provide the passing of parameters and avoid the need for saving and restoring register values.

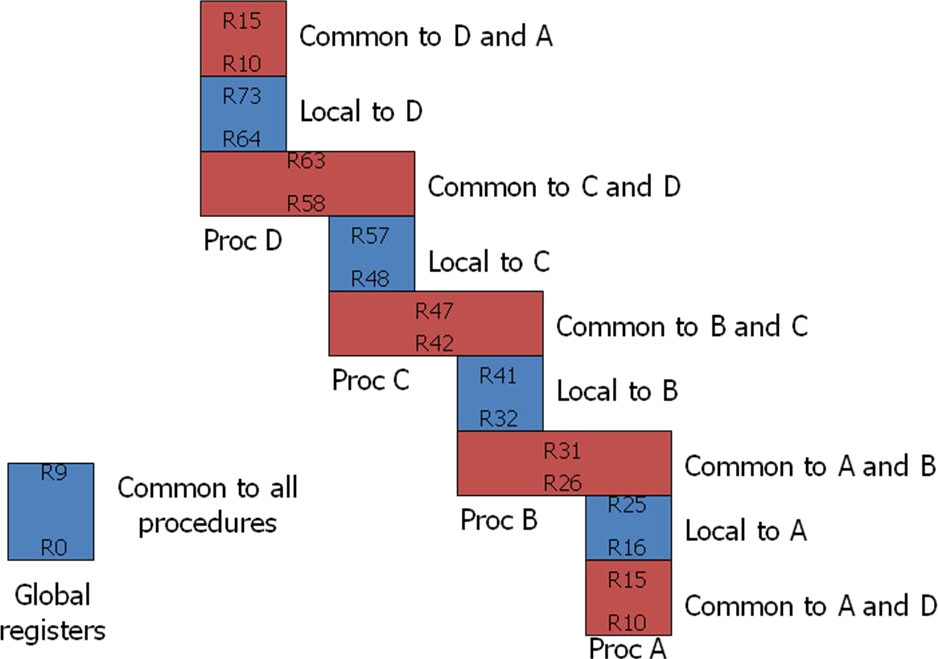

- The concept of overlapped register windows is illustrated in below figure.

- In general, the organization of register windows will have the following relationships:

Number of global registers = G

Number of local registers in each window = L

Number of registers common to two windows = C

Number of windows = W

The number of registers available for each window is calculated as followed:

Window size = L + 2C + G

The total number of registers needed in the processor is

Register file = (L + C)W + G

Fig: Overlapped Register Window

- A total of 74 registers

- Global Registers = 10 à common to all procedures

- 64 registers à divided into 4 windows A, B, C & D

- Each register window = 10 registers à local

- Two sets of 16 registers à common to adjacent procedures

Berkeley RISC I

- The Berkeley RISC I is a 32-bit integrated circuit

- It supports 32-bit address and either 8-, 16-, or 32-bit data.

- It has a 32-bit instruction format and a total of 31 instructions.

- There are three basic addressing modes: Register addressing, immediate operand, and relative to PC addressing for branch instructions.

- It has a register file of 138 registers; 10 global register and 8 windows of 32 registers in each

- The 32 registers in each window have an organization similar to overlapped register window.

Fig: Instruction Format of Berkeley RISC I

- Above figure shows the 32-bit instruction formats used for register-to-register instructions and memory access instructions.

- Seven of the bits in the operation code specify an operation, and the eighth bit indicates whether to update the status bits after an ALU operation.

- For register-to-register instructions :

- The 5-bit Rd field select one of the 32 registers as a destination for the result of the operation

- The operation is performed with the data specified in fields Rs and S2.

- Thus the instruction has a three-address format, but the second source may be either a register or an immediate operand.

- For memory access instructions:

- Rs to specify a 32-bit address in a register

- S2 to specify an offset

- Register R0 contains all 0’s, so it can be used in any field to specify a zero quantity

- The third instruction format combines the last three fields to form a 19-bit relative address Y and is used primarily with the jump and call instructions.

- The COND field replaces the Rd field for jump instructions and is used to specify one of 16 possible branch conditions.